LSIを構成するIP回路ブロックの開発

~新機能・高性能セルライブラリの構築による応用展開~

整理番号:2016-112

研究者名: 大塚 寛治(Kanji Ootsuka)

所 属: 連携研究センター 名誉教授、特別顧問、主幹研究員

専門分野:電気電子工学、電子・電気材料工学、電子デバイス・電子機器、

通信・ネットワーク工学

キーワード:電子材料工学、マイクロエレクトロニクス工学、コンピュータハードウェア工学

研究概要

当研究室は長年、実践で鍛えたベテラン技術者によるコンピュータアーキテクチャ、システム・回路設計、高速信号伝送・電源設計能力を備えています。最近のIP注1)として、検索エンジン、メモリ・論理共役コンピュータ、高解像度タッチパネルシステムがあります。また、技術として、28 Gbps(Gigabits per second)以上の低消費電力I/Oシステムがあります。

I/Oインターフェイスの各要素の基本となる回路・システム設計の一例を紹介します。

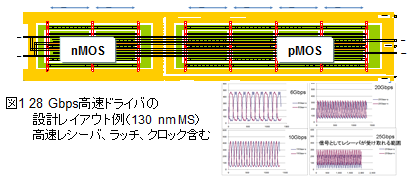

- 回路は全て既存IPを使わず、オリジナルなデバイス・回路設計(図1) 微細プロセスを採用しなくても28 Gbpsシステムが可能

- 最近の注目システム その1メモリ・論理共役回路(図2)人間の脳のニューロンと同様、回路そのものが論理であり、メモリであるダイナミックコンフィギュレーションの究極を行く回路

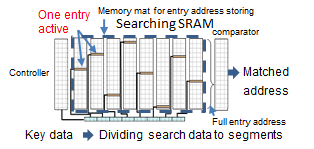

- 最近の注目システム その2 検索エンジン:Axonerve(図3)クラウドコンピューティングの時代になり、高速大容量ネットワーク(Internet環境)に必須のルータやスイッチに多用されている検索エンジンの一つContents Addresable Memory(CAM)の新アルゴリズムで、低電力エンジンもIPとして開発完了間近

注1):Intellectual Properties、半導体分野ではLSI(大規模集積回路)を構成する機能ブロックをいう

図2 最近の注目システムその1

メモリ・論理共役回路

図3 最近の注目システムその2

検索エンジン:Axonerve

応用例・用途

- 新機能・高性能セルライブラリ構築により、新しい電子制御装置の開発が可能

- アジアにおけるIEEE活動に多大に貢献により、Regional Contribution Awardを受賞(2014年)

研究設備

- 10 GHz以上のデジタル波形測定装置

- 20-50 GHzのベクトルネットワークアナライザなど高速信号系の測定装置